# **POS Motherboard**

INTEL PENTIUM M 760 2.0 GHz Processor INTEL CELERON M 370 1.5 GHz Processor (**F2-CPU Basic**)

All brand and product names mentioned in this document are trademarks of their respective owners.

The reproduction, transmission or use of this document or its contents is not permitted without express authority.

Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved. Delivery subject to availability; technical modifications possible. Copyright ©Wincor Nixdorf International GmbH, 2007

# Contents

| Introduction                               |    |

|--------------------------------------------|----|

| Highlights                                 | 2  |

| Mechanical Dimensions                      | 2  |

| Functional Blocks                          | 3  |

| Technical Data                             | 4  |

| Plug-in Cards Risercard                    | 7  |

| Block Diagram including connectors         | 8  |

| Mechanical Arrangement                     | 9  |

| Onboard Components                         | 10 |

| Microprocessors:                           | 10 |

| Graphics System                            | 10 |

| I/O Controller                             | 10 |

| Firmware HUB                               | 11 |

| Super I/O-Controller                       | 11 |

| Chrystalclear Sound fusion Audio Codec `97 | 11 |

| Stereo Amplifier                           | 11 |

| Clock Generator                            | 11 |

| Hardware Monitoring                        | 12 |

| Main Memory                                | 12 |

| 32Bit PCI Onboard Plug-In Module Interface | 13 |

| LAN 10/100 Interface                       | 13 |

| Serial Interfaces COM1, COM2*              | 13 |

| Keyboard / PS/2 MOUSE INTERFACE            | 13 |

| USB Interface                              | 13 |

| Hard Disk Interface Serial ATA (SATA)      | 14 |

| IDE Interface                              | 14 |

| Speaker                                    | 14 |

| Cash Drawer Interface                      | 14 |

| Fans                                       | 14 |

| Status Display Interface                   | 15 |

| Changing the CPU Battery                   | 16 |

| Operating Modes                            | 17 |

| General                                    | 17 |

| Normal Mode / Standby Mode                 | 17 |

| Switching on                               | 17 |

| Switching off                              | 17 |

| Power Failure                              | 17 |

| Connector Assignments                      | 18 |

| Connectors for external Connections     | 18 |

|-----------------------------------------|----|

| Serial Interfaces COM1, COM2* (ONBOARD) | 18 |

| Keyboard/Mouse Interface (external)     | 18 |

| USB Interface USB1, USB2 (Onboard)      | 18 |

| CRT Connection                          | 19 |

| TFT Connection                          | 19 |

| LAN Connection                          | 20 |

| Speaker out                             | 20 |

| Microphone                              | 20 |

| Connectors for internal Connections     | 21 |

| Main Memory                             | 21 |

| SATA1, SATA2                            | 24 |

| IDE                                     | 24 |

| CRT-Adapter                             | 25 |

| SDVO-Interface                          | 25 |

| PoweredUSB Adapter                      | 26 |

| USB 3-8                                 | 26 |

| PS/2 MOUSE                              | 26 |

| PCI-ONBOARD                             | 27 |

| Speaker                                 | 28 |

| Power Supply Unit                       | 28 |

| Power On                                | 28 |

| Status Display                          | 28 |

| FAN Connector 1                         | 29 |

| FAN Connector 2                         | 29 |

| POS Board                               | 30 |

| BIOS Setup                              | 31 |

| Standard BIOS Version                   | 31 |

| BIOS Menu Bar                           | 31 |

| Legend Bar                              | 32 |

| General Help                            | 33 |

| Scroll Bar                              | 33 |

| Sub-Menu                                | 33 |

| Info screen                             | 33 |

| Product name:                           | 34 |

| Bios version:                           |    |

| Ethernet MAC-Address:                   |    |

| System Main board Power Supply:         |    |

| M | ain Menu                                         | 34   |

|---|--------------------------------------------------|------|

|   | System Time [XX: XX: XX]                         | 34   |

|   | System Date [XX/XX/XXXX]                         | 34   |

|   | Primary & Secondary Master/Slave                 | 35   |

|   | SMART Monitoring                                 | 37   |

|   | Extended Memory: XXX MB                          | 37   |

| A | dvanced Menu                                     | . 37 |

|   | Reset Configuration Data [No]                    | . 37 |

|   | Speaker Volume [High]                            | 37   |

|   | Large Disk Access Mode [DOS]                     | . 37 |

|   | Legacy USB Support [Disabled]                    | . 38 |

|   | Internal LAN Controller [Enabled]                | . 38 |

|   | Onboard LAN Boot Prom [Disabled]                 | 38   |

|   | QuickBoot Mode [Disabled]                        | . 38 |

|   | Fan Control [Max Cooling]                        | . 38 |

|   | Chipset Configuration                            | 38   |

|   | SMART Device Monitoring [Disabled]               | 38   |

|   | Boot-Video device [Onboard]                      | . 38 |

|   | USB 2.0 Support [Enabled]                        | 39   |

|   | I/O Device Configuration                         | 39   |

|   | Serial port A [Enabled], Serial port B [Enabled] | 39   |

|   | Base I/O address                                 | 39   |

|   | Interrupt                                        | 39   |

|   | Touch Screen Routing [TFT Touch to COM2]         | 39   |

|   | DMI Event Logging                                | 39   |

|   | View DMI event log [Enter]                       | 40   |

|   | Clear all DMI event logs [No]                    | 40   |

|   | Event logging [Enabled]                          | 40   |

|   | Mark DMI events as read [Enter]                  | 40   |

| S | ecurity Menu                                     | 40   |

|   | Set Supervisor Password                          | 40   |

| Ρ | ower Menu                                        | 40   |

|   | After Power Failure [Stay off]                   | 41   |

|   | Wake-On-LAN [Disabled]                           | 41   |

|   | Wake-On-Modem Ring [Disabled]                    | 41   |

|   | Wake-On-Time [Disabled]                          | 41   |

|   | Hardware Monitor                                 | 41   |

| Boot Menu                       | . 42 |

|---------------------------------|------|

| Boot Order [Follow Setup Order] | . 42 |

| Exit Menu                       | . 42 |

| Exit Saving Changes             | . 42 |

| Exit Discarding Changes         |      |

| Load Setup Defaults             | . 43 |

| Discard Changes                 | . 43 |

| Test points codes               |      |

| Additional Test points codes    |      |

| bbreviations                    |      |

|                                 |      |

# Introduction

The F2-CPU Basic is the next step in the class of BEETLE Systems like BEETLE /NetPOS and BEETLE /iPOS.

The F2-CPU Basic Motherboard is a subset of the existing F2-CPU-Standard including DDR2-RAMs, but with smaller formfactor.

The following leading edge technologies are supported:

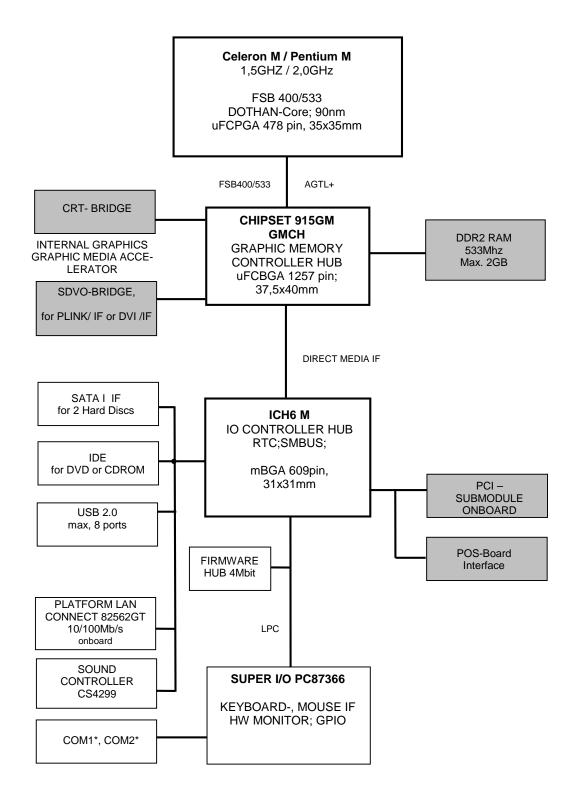

### **Microprocessors:**

INTEL CELERON M 370 1,5GHz Processor INTEL PENTIUM M 760 2GHz Processor

### Chipset:

- Platform with chipset 915GM Express

- Chipset with GMCH and ICH6M

### **Features**

- Frontside Bus up to 533Mhz

- 2 SATA I Interfaces for Harddisks

- Enhanced internal graphic with new Graphic interface (SDVO)

- Improvement of System Performance by internal Graphics and SATA I Interfaces

- Max 8 USB ports (USB1.1 and 2.0)

### **Highlights**

- LAN integrated onboard

- Use of available DDR2 RAM 533 (PC4200), 512Mbit technology

- Min. Main Memory 256MB; Max Main Memory 2GB

- Onboard PCI connector for PCI based Plug-in modules: Support of introduced Secondary CRT Controller and Secondary TFT Controller

- Mobile Processor Celeron/Pentium M allows the use of available PSU, Fan Technology and housings of the BEETLE family

- Jumperless motherboard

- Support of DVD (CD-ROM)

- SDVO Bridges for Panellink Interface and for DVI Interface

- CRT-Bridge with changed cable length

- New POS-Board

- No support of LPT1

- No support of Gameport

- No support of DVD Audio

- No support of WLAN

- No support of Floppydisk

- No support of Line In

- No support of COM3,4 module

- No support of Power USB Adapter

- No support of Sandwich Card with NVRAM

- No support of 7-segment-LED-display for BIOS debugging

- No support of Risercard with PCI-Standard / PCI-Express connectors

**Attention**: Only TFT- displays with DDC (like BA72A-2 and BA73A-2) will be supported. Because older displays are not supported furthermore, no jumpers on the motherboard are needed.

## **Mechanical Dimensions**

#### Mechanical dimensions of F2-CPU Basic:

The bracket/ connector outlets of the motherboard are similar to E1-CPU-Basic. The formfactor of the bareboard is also similar to this CPU. Therefore the F2-CPU BasicC is able to support the BEETLE/systems B/NetPOS and B/iPOS.

### Long term availability:

CELERON/PENTIUM M and chipset 915GM are supported by the INTEL IPD (Infrastructure Processor Devision) "Embedded" Group. In this way the longtime- availability is guaranteed.

### Operating systems/BIOS:

The F2-CPU Basic has complete PC functionality and supports the following operating systems: WIN/XP, WIN/XP Embedded and Linux. Features of PnP, ACPI, DMI are implemented. The size of the firmware Hub is 4Mbit.

2

### **Functional Blocks**

### **Technical Data**

Supported Systems: BEETLE /NetPOS, BEETLE/iPOS

· Architecture: PC-AT compatible and POS - specific

functional units

**Operating Modes:** Normal Mode, Power Save Mode

**Power Management** ACPI 1.0, APM 1.2

WIN XP, WIN XP Embedded, LINUX Operating Systems:

INTEL<sup>R</sup> Celeron<sup>R</sup> M 370 1,5GHZ processor **Microprocessor:**

(478 Pin uFCPGA package,

90 nm technology)

INTEL<sup>R</sup> Pentium<sup>R</sup> M 760 2,0GHz processor

(478 Pin uFCPGA package,

90 nm technology)

Chipset: INTEL chipset 915GM/ICH6M:

Graphic and Memory Controller Hub (GMCH) with

the following functions:

Memory Cntrl. supports DDR2 SDRAM with

533MHz System memory bus,

UMA (Unified Memory Architecture),

Graphic supports 2D and 3D and video streams,

Plug and Display Functionality

Video memory with INTEL Embedded Graphics

Driver max. 128MB (Dynamic Video Memory

Technology)

Max. Resolution CRT:

1600 x 1200 x 32 Bit@ 85Hz

2048 x 1536 x 32 Bit@ 75Hz

Max. Resolution TFT:

1600 x 1200 x 24 Bit@ 60Hz

I/O Controller Hub 6 (ICH6M) with the following

functions:

LAN 10/100 Cntrl., SATA - Cntrl., IDE-Cntrl. w/ UDMA, USB Cntrl. UHCI and EHCI, Interrupt-Cntrl., DMA-Cntrl., LPC-Interface, RTC, SMBus-

Host interface

NS87366 with the following functions:

Floppy Cntrl., 2 Serial Ports, Keybd. Interface,

PS/2 Mouse Interface, HW- Monitor,

Intrusion Logic

Super I/O:

4

Sound controller: CS4299 Audio Codec controller with the

following AC`97 functions:

20 Bit Stereo DAC and 18 Bit Stereo ADC Mono

Mic Input (MIC)

Stereo Line-Level Output

Sound connection: Mono Microphone Input, Stereo Speaker

Output (2 x 1,25 W @ 8 Ohm)

Main Memory:

256 MB up to max. 2GB, 2 DIMM – sockets

(240pin), 1.8 V

DDR2 SDRAM technology based on 512Mb technology, unbuffered non ECC, DDR2-533 Standard

DIMM

Height up to 35 mm

POS-Board Interface:

PCI-Bus (32 bit interface, 33MHz)

BIOS: Firmware Hub: 4MB

512KB Flash Memory, Phoenix BIOS, PnP,

PCI Rev.1.0A, DMI -support

Battery: 3 V Lithium for RTC and SIO

Type: Sanyo CR2032, 220 mAh

System Bus Frequency 400/533MHzRAM Bus Frequency: 400/533 MHz

PCI Bus Frequency:

PCI 2.1, 33 MHz

Wake On feature: Wake On LAN,

Wake On MODEM, Wake On Time

Keyboard connection:

PC-AT compatible

PS/2-Mouse connection: via Y-cable together with keyboard,

optional internal connection

Serial interfaces: COM1\*, COM2\*

(COM3,4,6 with POS-Board)

• Loudspeaker: AT-compatible,

volume control defined by BIOS Setup in three

steps: high-, medium-, low volume

compatible; foil connector

• DVD connection (IDE): Local Bus IDE interface,

for 2 drives, PIO Mode 0 - Mode 4, ULTRA DMA Mode 0 - Mode 3

2mm connector,

Hard disk connection (SATA I): 2 ports , 1.5Gb/s

• USB connection: general: USB1.1, USB 2.0

USB1, 2: Standard 2 port connector, series A

USB 3,4,5,6,7,8: 1 x 6 pin header

Cash Drawer connection:

1 cash drawer can be connected.

Connection via RJ12 connector on POS-Board

PCI Plug-in card interface:

32 bit interface, 33 MHz

Status display connection: support for LEDs: Power On and HD activity

Intrusion sensor logic: dependent on BEETLE system, BIOS support

Current Consumption: (F2-Basic with 2GB Ram)

> +3,3 V tbd + 5 V tbd + 12 V tbd

Max. Current for keyboard +5V:500 mA

Max. Current per port (for COM1\*,2\*) +12V: 600 mA

Max. Current in total (for COM1\*,2\*) +12V: 900 mA

Max. Current per port (for COM1\*,2\*) + 5V: 300 mA

Max. Current in total (for COM1\*,2\*)

+ 5V: 500 mA

Max. Current per port

Standard USB1, USB2 + 5V: 500 mA

Max. Current in total Standard USB1, USB2 + 5V: 2,0 A

Fuses (Polyswitches):+5V: COM1\*, COM2\*,

USB1, USB2, Keyboard, Mouse

• +12V: COM1\*, COM2\*

Board Dimensions: about 190mm x210mm

# **Plug-in Cards Risercard**

The following Plug-in modules are available and they may be used on the F2-CPU Basic.

- Secondary CRT Controller

- Secondary TFT Controller

- SDVO Bridge for PLink IF and DVI

- CRT Bridge with new cable length

- New POS-Board

The following Plug-in modules may not be used:

- LAN module (INTEL)

- LAN module(REALTEK)

- WLAN module

- USBplus adapter (12V) (USB 2.0)

- USBplus adapter (24V) (USB 2.0)

- COM3\*,COM4\* adapter (PnP)

- Risercard with PCI Standard Interfaces

- NVRAM Add-On-Module

- Optional 7 segment LED display

- Optional Risercard with PCIe 1x

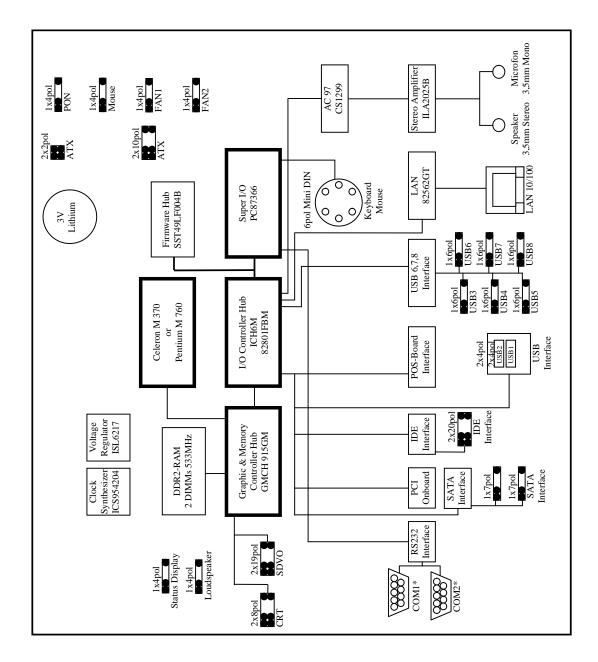

# **Block Diagram including connectors**

Main board F2 CPU Basic

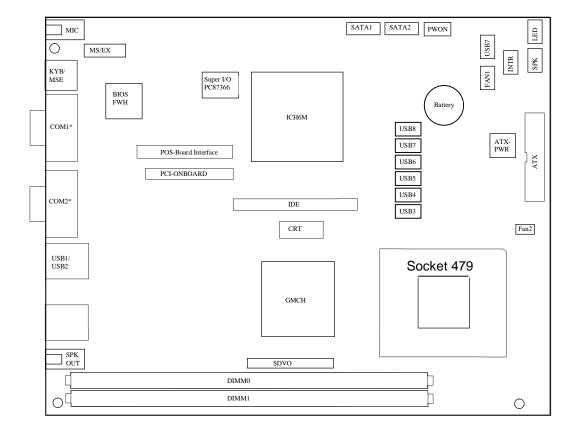

# **Mechanical Arrangement**

The CPU comprises of the printed circuit board with connectors for all external peripheral connections and for installing the optional plug-in cards.

# **Onboard Components**

### **Microprocessors:**

INTEL PENTIUM M 760 2.0 GHz Processor INTEL CELERON M 370 1.5 GHz Processor

### **Graphics System**

The GMCH integrates a system memory DDR SDRAM controller that supports 256MB up to 2GB memory (400/533MHz). It also contains a graphic controller for enhanced integrated 2D and 3D graphics performance.

The GMCH drives via a CRT Bridge a standard CRT monitor up to a resolution of 2048x1536 pixel with 32-bit at 60 Hz.

For connecting TFT LCDs the GMCH provides a Digital Video Out interface to implement a resolution up to 1600 x 1200 pixels with 24-bit. The DVO interface is driving the TFT Panellink Bridge and has low voltage high-speed signaling to allow operation at higher frequencies.

The GMCH has a core voltage of 1.05 V; the system memory operates with 1,8 V.

The GMCH is housed in a 1257 pin uFCBGA package.

### I/O Controller

The ICH6M (82801FBM) provides extensive I/O support. Functions and capabilities include:

- PCI Interface

- PCI Express Interface

- Enhanced DMA controller, Interrupt controller and Timer functions

- Serial ATA Interface

- Integrated IDE controller supports Ultra ATA 100/66/33

- USB host interface (EHCl Controller with 8 ports Vers. 2.0, 4 x UHCl Controller with 2 ports each Vers. 1.1)

- Integrated LAN controller 10/100 Mbit/sec

- System Management Bus (SMB)

- AC97 Vers. 2.3 support for audio and modem

- Low Pin Count (LPC) interface

- Firmware Hub (FWH) interface support

The ICH6M is housed in a 609 mBGA package.

### Firmware HUB

This device is designed for BIOS applications and contains 1MB Flash memory organized in 8 x 1024Kb blocks. The hardware features of this device include a random number generator, five general purpose inputs, register based block locking and hardware based locking. It operates under the LPC/FWH interface protocol.

The Firmware Hub is housed in a 32pin PLCC.

### Super I/O-Controller

The PC87366 is a Low Pin Count Interface-based highly integrated Super I/O and provides the following functions:

- Two 16C550 UARTs

- Keyboard and PS/2 Mouse Controller

- Enhanced Hardware Monitor

- Fan Speed Controller

- 40 General Purpose I/O pins

The PC87366 is housed in a 128 pin QFP package.

## **Chrystalclear Sound fusion Audio Codec `97**

The CS4299 is a Codec with AC´97 features. It is implemented as 20 bit stereo DAC and 18 bit stereo ADC with sample rate conversion. The F2- CPU uses one microphone mono input and the line stereo output which will drive the stereo amplifier TEA2025B.

The CS4299 is housed in a 48 pin LQFP package.

### **Stereo Amplifier**

The TEA2025B is a stereo audio power amplifier capable of delivering typically 1.25 Watt per channel of continuous average power to an 8 Ohm load with 0.1% (THD) using a 12 V power supply. The TEA2025B is housed in a 16 pin DIL package.

#### **Clock Generator**

The ICS Clock Generator ICS954204 is designed for the INTEL "Alviso" chipset and provides all clocks for the chipset, microprocessor, PCI interface, SATA interface, USB interface and Super I/O. The RAM clocks are provided by the GMCH.

The ICS954204 provides an I<sup>2</sup>C (2 wire) interface to program the internal registers. For EMI reduction the synthesizer provides integrated LCD spread spectrum.

The ICS954204 is housed in 56 pin TSSOP package.

## **Hardware Monitoring**

The PC87366 contains an enhanced Hardware Monitor which will be used for sensing/ controlling the following signals:

- · the temperature of the processor

- Core voltage of the processor

- 3.3V system voltage

- 1.8V system voltage for system memory

- 1.5V core voltage

- 5V system voltage

- · Battery voltage 3V

- 12V system voltage

- -12V system voltage

- Fan tachometer signal of processor fan, system fan and PSU fan

- Fan PWM signal for processor fan and system fan

## **Main Memory**

The F2-CPU Basic provides two DIMM (240 Pin) sockets for connecting DDR2 modules in unbuffered SDRAM technology from 256MB (1 x 256MB) up to 2 Bytes (2x 1GB). DDR2 DIMMs with different sizes are usable.

One or both DDR2 DIMM may be assembled. The DDR2 DIMMs are unbuffered 1.8V memory modules.

|          | Main Memory |                 |

|----------|-------------|-----------------|

| Socket 1 | Socket 2    | Total Capacity  |

| 32MBx64  | (32MBx64)   | 256 MB (512 MB) |

| 64MBx64  | (64MBx64)   | 512 MB (1 GB)   |

| 128MBx64 | (128MBx64)  | 1 GB( 2 GB)     |

Any combinations of the DIMMs are allowed.

### 32Bit PCI Onboard Plug-In Module Interface

The Onboard 32 bit PCI bus interface is provided to assemble PCI bus based Plug-In-Modules.

The PCI bus interface contains all signals necessary for a PCI Master module. Furthermore, the WOL interface is provided, i.e. the Standby Voltage and the Wake On signal are available.

### LAN 10/100 Interface

The ICH6M contains the control logic for the LAN interface and together with the Platform LAN Connect (82562GT) it provides the LAN 10/100 interface. The connector is soldered onboard and provides two LEDs for traffic information.

### Serial Interfaces COM1, COM2\*

COM1 is the standard serial interface controlled by the Super I/O PC87366. All signals incl. the modem signals RI and DCD are available on the 9 pin DSUB connector (male).

The I/O assignments of the serial port COM2\* deviate from the standard in the way that it is equipped with system voltages of +5V and +12V instead of the signals RI (M3) and DCD (M5). The channel is connected via 9-pin D-sub (female) socket because of the additional system voltages.

### **Keyboard / PS/2 MOUSE INTERFACE**

The keyboard controller is part of the Super I/O. The keyboard interface - as well as the PS/2 – mouse interface - is available on the Mini DIN connector. Using both of them requires a Y- adapter-cable.

#### **USB** Interface

The USB interface supplied by the ICH6M contains one EHCI controller with 8 downstream ports providing high speed data rate (480Mb/sec, USB 2.0) and 4 UHCI controllers (2 ports each) for full and low speed data rate (12 Mb/sec and 1.5Mb/sec, USB1.1).

USB ports 1 and 2 are available on the main board. The USB connector is type Stack A.

USB ports 3- 8 are available on 1 x 6 pin headers. Connection to the rear - or front side of the BEETLE- system requires a special cable.

### Hard Disk Interface Serial ATA (SATA)

There are two Serial ATA Ports with 1.5 GB/s, (Type 1) available.

#### **IDE Interface**

The CPU features a UDMA IDE interface for connecting up to 2 ATA compatible drives. The I/O addresses meet the AT standard. The connector on the CPU is the Standard 2x22-pin header (2-mm arrangement) for connecting a CD-ROM or DVD drive. All parameters of the drives are read by the BIOS automatically and stored in the BIOS setup parameter set. The F2-CPU Basic supports IDE drives up to PIO-Mode 4 and UltraDMA Mode 2.

### Speaker

The CPU is equipped with control logic circuitry for a speaker. The volume of the speaker may be defined in the BIOS Setup. It may be set to high, medium or low; the default setting is high. The speaker itself is located in the housing of the BEETLE system.

#### **Cash Drawer Interface**

The logic for controlling the cash drawer is placed on the POS-board. The I/O assignment is compatible to other CPU's in BEETLE systems.

| Input031x/ bit6 $(x = 0 - 7)$ | LAZU1N=0<br>LAZU1N=1 | Cash drawer 1 closed or not present<br>Cash drawer 1 open |

|-------------------------------|----------------------|-----------------------------------------------------------|

| Input031x/ bit7 $(x = 0 - 7)$ | LAZU2N=0<br>LAZU2N=1 | Cash drawer 2 closed or not present Cash drawer 2 open    |

The length of the pulse for opening the cash drawer has to be nominal 130msec. There must be a time interval of 6 seconds between two outputs (charging time of capacitor in the cash-drawer electronic circuitry).

### **Fans**

The F2-CPU Basic supports Fan speed control by pulse width modulation (PWM). Therefore, 2 connectors with additional PWM signal for each a system's fan are provided. PWM will be done by BIOS depending of the measured temperature.

The tacho lines are monitored by Hardware and may be reported via BIOS SETUP and DMI.

| FAN1 | System Fan |

|------|------------|

| FAN2 | System Fan |

# **Status Display Interface**

| STATUS OF SYSTEM                 | POWER-LED at<br>FRONT | HD-LED at<br>FRONT | REMARKS                                               |

|----------------------------------|-----------------------|--------------------|-------------------------------------------------------|

| OFF                              |                       |                    | AC OFF                                                |

| STANDBY<br>AND SOFTOFF           |                       |                    | AC ON                                                 |

| POWER ON                         |                       |                    | SYSTEM VOLTAGES<br>3,3V; 5V; 12V; 24V<br>AVAILABLE    |

| BIOS START                       |                       |                    | BIOS START IS<br>WORKING<br>PROPERLY                  |

| BIOS<br>PREBOOT<br>PHASE<br>DONE |                       |                    | CONTROL OF THE<br>LED WILL BE<br>DONE BY HD<br>ACCESS |

| HD -ACCESS                       |                       |                    | SHORT TIME ON<br>DURING ACCESS OF<br>HD DISK OR CDROM |

Green

Yellow

# **Changing the CPU Battery**

The BEETLE POS systems are equipped with a lithium battery on the CPU board (see page 9) to ensure data retention, the time and the setup parameters. The battery should be changed approximately every five years.

✓ When inserting the new battery, make sure the polarity is correct. This is marked in the socket. Incorrect replacement of the battery may lead to the danger of explosion.

The battery is located in a socket in the CPU. To gain access to the battery, proceed as described in the according chapters of your BEETLE **User Manual**.

#### See:

http://www.wincor-nixdorf.com/internet/uk/Services 26Support/Support/TechnicalSupport/POSSystems/Manuals/index.html

✓ The lithium battery must be replaced only by identical batteries or types recommended by Wincor Nixdorf International.

You can return the used batteries to your Wincor Nixdorf International sales outlet.

Batteries containing harmful substances are marked accordingly. The chemical denotations are as follows: CD = Cadmium; Pb = Lead, Li = Lithium.

This symbol on a battery tells you that batteries containing harmful substances must not be disposed of as household waste. Follow the country specific laws and regulations. Within the European Union you are legally bound to return these batteries to the service organization where you purchased the new battery.

The setup parameters must be reset each time the battery has been changed.

# **Operating Modes**

#### General

The F2-CPU Basic provides power management functions dependent on the installed Operating system. The BIOS supports ACPI 1.0 and APM 1.2. (for details see the BIOS description)

### Normal Mode / Standby Mode

### Switching on

Power Supplies w/ and w/o UPS functionality will be used in F2-CPU Basic based systems. Connecting the PSU via AC line the Standby voltage P5VSB is supplied and the system is ready to be switched on (Standby mode). There are several possibilities to switch on the system.

• The "regular" way to switch on the system is to activate the pushbutton at the front side of the system.

Shortly pressing the pushbutton will switch on the system.

- Wake On LAN is another possibility to switch on the system.

- Last not least the RTC can be used to switch on the system.

### Switching off

The system may be switched off either by activating the pushbutton at the front side of the system or under Software Control.

Pressing the pushbutton longer than 4 seconds will switch off the system.

#### **Power Failure**

If the main power fails (AC input) for longer than 20 msec, the loss of Standby Voltage results in powering down the system.

After the main power returned the system responds depending on the BIOS Setup setting. If in the BIOS Setup "Restore" is chosen, the system enters the state before Power failure. If in the BIOS Setup "Stay Off" is chosen, the system stays off. If "Follow A/C Power" is chosen in the BIOS Setup, the system enters the "On state" after the main power returned. The power button is disabled.

# **Connector Assignments**

### **Connectors for external Connections**

## Serial Interfaces COM1, COM2\* (ONBOARD)

X15, 9-pin D-sub connector, male X16, 9-pin D-sub connector (voltages assigned), female

| PIN# | COM1  | COM2*  |  |

|------|-------|--------|--|

| 1    | DCD1F | P12VFS |  |

| 2    | RXD1F | RXD2F  |  |

| 3    | TXD1F | TXD2F  |  |

| 4    | DTR1F | DTR2F  |  |

| 5    | GNDF  | GNDF   |  |

| 6    | DSR1F | DSR2F  |  |

| 7    | RTS1F | RTS2F  |  |

| 8    | CTS1F | CTS2F  |  |

| 9    | RI1F  | P5VFS  |  |

### **Keyboard/Mouse Interface (external)**

X35, 6-pin mini DIN connector (PS/2-compatible), female

| PIN# | SIGNAL |

|------|--------|

| 1    | KDF    |

| 2    | MSDAF  |

| 3    | GND    |

| 4    | P5VFKY |

| 5    | KCF    |

| 6    | MSCKF  |

### **USB Interface USB1, USB2 (Onboard)**

X36, 2 x 4 pin USB Standard connector, Series Stack A, male

| PIN# | USB1     | USB2     |

|------|----------|----------|

| 1    | P5VFUS1F | P5VFUS2F |

| 2    | U1D-     | U2D-     |

| 3    | U1D+     | U2D+     |

| 4    | GND_U    | GND_U    |

18

### **CRT Connection**

This connector is not part of the F2-CPU Basic. It is part of the CRT-Adapter and, if populated, available at the rear side of the cabinet.

15-pin HDD sub connector (CRT), female

| PIN# | SIGNALS VID |

|------|-------------|

| 1    | RED         |

| 2    | GREEN       |

| 3    | BLUE        |

| 4    | NC          |

| 5    | GND         |

| 6    | GND         |

| 7    | GND         |

| 8    | GND         |

| 9    | 5VFU        |

| 10   | GND         |

| 11   | NC          |

| 12   | DDCSDA      |

| 13   | FHSYNC      |

| 14   | FVSYNC      |

| 15   | DDCSCL      |

### **TFT Connection**

This connector is not part of the F2-CPU Basic. It is part of the SDVO Bridge and, if populated, available at the rear side of the cabinet.

40 pin Mini Delta Ribbon (TFT), female

| PIN# | SIGNALS TFT | PIN# | SIGNALS TFT |

|------|-------------|------|-------------|

| 1    | GND         | 2    | TX2+        |

| 3    | TX2 Shield  | 4    | TX2-        |

| 5    | P12V LCD    | 6    | GND         |

| 7    | TX1+        | 8    | GND         |

| 9    | TX1-        | 10   | GND         |

| 11   | P12V LCD    | 12   | P12V        |

| 13   | P12V LCD    | 14   | TXD         |

| 15   | GND         | 16   | RXD         |

| 17   | NC          | 18   | TX0+        |

| 19   | GND         | 20   | TX0-        |

| 21   | P5V LCD     | 22   | P5V LCD     |

| 23   | TXC+        | 24   | GND         |

| 25   | TXC-        | 26   | SP Out      |

| 27   | SC DDC      | 28   | SD DDC      |

| 29   | NC          | 30   | NC          |

| 31   | NC          | 32   | NC          |

| 33   | NC          | 34   | NC          |

| 35   | NC          | 36   | NC          |

| 37   | NC          | 38   | NC          |

| 39   | NC          | 40   | NC          |

|      |             |      |             |

## **LAN Connection**

X26, 8 pin RJ45 (LAN), female

| PIN# | SIGNALS | SIGNALS |  |  |

|------|---------|---------|--|--|

| 1    | TX +    |         |  |  |

| 2    | TX -    |         |  |  |

| 3    | NC      |         |  |  |

| 4    | NC      |         |  |  |

| 5    | NC      |         |  |  |

| 6    | NC      |         |  |  |

| 7    | RX+     |         |  |  |

| 8    | RX-     |         |  |  |

## Speaker out

X39, 5-pin, 3.5mm female connector

| PIN# | SIGNALS OUT |  |

|------|-------------|--|

| 1    | AGND        |  |

| 2    | LOLAF       |  |

| 3    | NC          |  |

| 4    | LORAF       |  |

| 5    | NC          |  |

## Microphone

X38, 5-pin, 3.5mm female connector

| PIN# | SIGNALS MIC |  |

|------|-------------|--|

| 1    | GND         |  |

| 2    | MICF        |  |

| 3    | NC          |  |

| 4    | VREFOUT     |  |

| 5    | NC          |  |

# **Connectors for internal Connections**

# **Main Memory**

X1, X2, 2 x 120 pin micro edge connector

| PIN# | · ·    |  |

|------|--------|--|

| 1    | RAMREF |  |

| 2    | GND    |  |

| 3    | DQ0    |  |

| 4    | DQ1    |  |

| 5    | GND    |  |

| 6    | DQS0#  |  |

| 7    | DQS0   |  |

| 8    | GND    |  |

| 9    | DQ2    |  |

| 10   | DQ3    |  |

| 11   | GND    |  |

| 12   | DQ8    |  |

| 13   | DQ9    |  |

| 14   | GND    |  |

| 15   | DQS1#  |  |

| 16   | DQS1   |  |

| 17   | GND    |  |

| 18   | n.c.   |  |

| 19   | n.c.   |  |

| 20   | GND    |  |

| 21   | DQ10   |  |

| 22   | DQ11   |  |

| 23   | GND    |  |

| 24   | DQ16   |  |

| 25   | DQ17   |  |

| 26   | GND    |  |

| 27   | DQS2#  |  |

| 28   | DQS2   |  |

| 29   | GND    |  |

| 30   | DQ18   |  |

| 31   | DQ19   |  |

| 32   | GND    |  |

| 33   | DQ24   |  |

| 34   | DQ25   |  |

| 35   | GND    |  |

| 36   | DQS3#  |  |

| 37   | DQS3   |  |

| 38   | GND    |  |

| 39   | DQ26   |  |

| 40   | DQ27   |  |

| 41   | GND    |  |

| 42   | n.c.   |  |

| 43   | n.c.   |  |

| 44   | GND    |  |

| PIN# | SIGNALS DIMM0, 1 |  |

|------|------------------|--|

| 45   | n.c.             |  |

| 46   | n.c.             |  |

| 47   | GND              |  |

| 48   | n.c.             |  |

| 49   | n.c.             |  |

| 50   | GND              |  |

| 51   | P1V8             |  |

| 52   | CKE0             |  |

| 53   | P1V8             |  |

| 54   | BS2              |  |

| 55   | n.c.             |  |

| 56   | P1V8             |  |

| 57   | MA11             |  |

| 58   | MA7              |  |

| 59   | P1V8             |  |

| 60   | MA5              |  |

| 61   | MA4              |  |

| 62   | P1V8             |  |

| 63   | MA2              |  |

| 64   | P1V8             |  |

| 65   | GND              |  |

| 66   | GND              |  |

| 67   | P1V8             |  |

| 68   | n.c.             |  |

| 69   | P1V8             |  |

| 70   | MA10             |  |

| 71   | BS0              |  |

| 72   | P1V8             |  |

| 73   | WE#              |  |

| 74   | CAS#             |  |

| 75   | P1V8             |  |

| 76   | CS1#             |  |

| 77   | ODT1             |  |

| 78   | P1V8             |  |

| 79   | GND              |  |

| 80   | DQ32             |  |

| 81   | DQ33             |  |

| 82   | GND              |  |

| 83   | DQS4#            |  |

| 84   | DQS4             |  |

| 85   | GND              |  |

| 86   | DQ34             |  |

| 87   | DQ35             |  |

| 88   | GND              |  |

| 89   | DQ40             |  |

|      |                  |  |

| PIN# | SIGNALS DIMMO, 1 |  |  |

|------|------------------|--|--|

| 90   | DQ41             |  |  |

| 91   | GND              |  |  |

| 92   | DQS5#            |  |  |

| 93   | DQS5             |  |  |

| 94   | GND              |  |  |

| 95   | DQ42             |  |  |

| 96   | DQ43             |  |  |

| 97   | GND              |  |  |

| 98   | DQ48             |  |  |

| 99   | DQ49             |  |  |

| 100  | GND              |  |  |

| 101  | GND              |  |  |

| 102  | n.c.             |  |  |

| 103  | GND              |  |  |

| 104  | DQS6#            |  |  |

| 105  | DQS6             |  |  |

| 106  | GND              |  |  |

| 107  | DQ50             |  |  |

| 108  | DQ51             |  |  |

| 109  | GND              |  |  |

| 110  | DQ56             |  |  |

| 111  | DQ57             |  |  |

| 112  | GND              |  |  |

| 113  | DQS7#            |  |  |

| 114  | DQS7             |  |  |

| 115  | GND              |  |  |

| 116  | DQ58             |  |  |

| 117  | DQ59             |  |  |

| 118  | GND              |  |  |

| 119  | SMBDA            |  |  |

| 120  | SMBCL            |  |  |

| 121  | GND              |  |  |

| 122  | DQ4              |  |  |

| 123  | DQ5              |  |  |

| 124  | GND              |  |  |

| 125  | DM0              |  |  |

| 126  | n.c.             |  |  |

| 127  | GND              |  |  |

| 128  | DQ6              |  |  |

| 129  | DQ7              |  |  |

| 130  | GND              |  |  |

| PIN# | SIGNALS DIMM0, 1 |  |  |

|------|------------------|--|--|

| 131  | DQ12             |  |  |

| 132  | DQ13             |  |  |

| 133  | GND              |  |  |

| 134  | DM1              |  |  |

| 135  | n.c.             |  |  |

| 136  | GND              |  |  |

| 137  | CK0              |  |  |

| 138  | CK0#             |  |  |

| 139  | GND              |  |  |

| 140  | DQ14             |  |  |

| 141  | DQ15             |  |  |

| 142  | GND              |  |  |

| 143  | DQ20             |  |  |

| 144  | DQ21             |  |  |

| 145  | GND              |  |  |

| 146  | DM2              |  |  |

| 147  | n.c.             |  |  |

| 148  | GND              |  |  |

| 149  | DQ22             |  |  |

| 150  | DQ23             |  |  |

| 151  | GND              |  |  |

| 152  | DQ28             |  |  |

| 153  | DQ29             |  |  |

| 154  | GND              |  |  |

| 155  | DM3              |  |  |

| 156  | n.c.             |  |  |

| 157  | GND              |  |  |

| 158  | DQ30             |  |  |

| 159  | DQ31             |  |  |

| 160  | GND              |  |  |

| 161  | n.c.             |  |  |

| 162  | n.c.             |  |  |

| 163  | GND              |  |  |

| 164  | n.c.             |  |  |

| 165  | n.c.             |  |  |

| 166  | GND              |  |  |

| 167  | n.c.             |  |  |

| 168  | n.c.             |  |  |

| 169  | GND              |  |  |

| 170  | P1V8             |  |  |

| 171  | CKE1             |  |  |

| PIN# | SIGNALS DIMMO, 1 |  |  |

|------|------------------|--|--|

| 172  | P1V8             |  |  |

| 173  | n.c.             |  |  |

| 174  | n.c.             |  |  |

| 175  | P1V8             |  |  |

| 176  | MA12             |  |  |

| 177  | MA9              |  |  |

| 178  | P1V8             |  |  |

| 179  | MA8              |  |  |

| 180  | MA6              |  |  |

| 181  | P1V8             |  |  |

| 182  | MA3              |  |  |

| 183  | MA1              |  |  |

| 184  | P1V8             |  |  |

| 185  | CK2              |  |  |

| 186  | CK2#             |  |  |

| 187  | P1V8             |  |  |

| 188  | MA0              |  |  |

| 189  | P1V8             |  |  |

| 190  | BS1              |  |  |

| 191  | P1V8             |  |  |

| 192  | RAS#             |  |  |

| 193  | CS0#             |  |  |

| 194  | P1V8             |  |  |

| 195  | ODT0             |  |  |

| 196  | MA13             |  |  |

| 197  | P1V8             |  |  |

| 198  | GND              |  |  |

| 199  | DQ36             |  |  |

| 200  | DQ37             |  |  |

| 201  | GND              |  |  |

| 202  | DM4              |  |  |

| 203  | n.c.             |  |  |

| 204  | GND              |  |  |

| 205  | DQ38             |  |  |

| 206  | DQ39             |  |  |

| 207  | GND              |  |  |

| 208  | DQ44             |  |  |

| 209  | DQ45             |  |  |

| 210  | GND              |  |  |

| PIN# | SIGNALS DIMMO, 1 |  |  |

|------|------------------|--|--|

| 211  | DM5              |  |  |

| 212  | n.c.             |  |  |

| 213  | GND              |  |  |

| 214  | DQ46             |  |  |

| 215  | DQ47             |  |  |

| 216  | GND              |  |  |

| 217  | DQ52             |  |  |

| 218  | DQ53             |  |  |

| 219  | GND              |  |  |

| 220  | CK1              |  |  |

| 221  | CK1#             |  |  |

| 222  | GND              |  |  |

| 223  | DM6              |  |  |

| 224  | n.c.             |  |  |

| 225  | GND              |  |  |

| 226  | DQ54             |  |  |

| 227  | DQ55             |  |  |

| 228  | GND              |  |  |

| 229  | DQ60             |  |  |

| 230  | DQ61             |  |  |

| 231  | GND              |  |  |

| 232  | DM7              |  |  |

| 233  | n.c.             |  |  |

| 234  | GND              |  |  |

| 235  | DQ62             |  |  |

| 236  | DQ63             |  |  |

| 237  | GND              |  |  |

| 238  | P3V3C            |  |  |

| 239  | GND              |  |  |

| 240  | GND              |  |  |

# SATA1, SATA2

X42, X43, 1 x 7 pin Header

| PIN# | SIGNALS SATA1 | PIN# | SIGNALS SATA2 |

|------|---------------|------|---------------|

| 1    | GND           | 1    | GND           |

| 2    | SATA0TXP      | 2    | SATA2TXP      |

| 3    | SATA0TXN      | 3    | SATA2TXN      |

| 4    | GND           | 4    | GND           |

| 5    | SATA0RXN      | 5    | SATA2RXN      |

| 6    | SATA0RXP      | 6    | SATA2RXP      |

| 7    | GND           | 7    | GND           |

## IDE

X23, 2 x 22-pin header, 2mm

| PIN# | SIGNALS IDE1 PIN | N # | SIGNALS IDE1 |

|------|------------------|-----|--------------|

| 1    | IDERESN          | 2   | GND          |

| 3    | IDE_DD7          | 4   | IDE_DD8      |

| 5    | IDE_DD6          | 6   | IDE_DD9      |

| 7    | IDE_DD5          | 8   | IDE_DD10     |

| 9    | IDE_DD4          | 10  | IDE_DD11     |

| 11   | IDE_DD3          | 12  | IDE_DD12     |

| 13   | IDE_DD2          | 14  | IDE_DD13     |

| 15   | IDE_DD1          | 16  | IDE_DD14     |

| 17   | IDE_DD0          | 18  | IDE_DD15     |

| 19   | GND              | 20  | KEY          |

| 21   | IDE_DDREQ        | 22  | GND          |

| 23   | IDE_DIOW#        | 24  | GND          |

| 25   | IDE_DIOR#        | 26  | GND          |

| 27   | IDE_IODRY        | 28  | GND          |

| 29   | IDE_DDACK#       | 30  | GND          |

| 31   | IDE_IRQ          | 32  | HIGH         |

| 33   | IDE_DA1          | 34  | P66DET       |

| 35   | IDE_DA0          | 36  | IDE_DA2      |

| 37   | IDE_DCS1N        | 38  | IDE_DCS3N    |

| 39   | IDE_LED          | 40  | GND          |

| 41   | VCC              | 42  | VCC          |

| 43   | GND              | 44  | GND          |

# **CRT-Adapter**

X72, 2 x 8 pin Berg Header

| PIN# | SIGNALS CRT PIN# | SIGI | NALS CRT   |

|------|------------------|------|------------|

| 1    | CRT_RED          | 2    | VCC        |

| 3    | CRT_GREEN        | 4    | VCC        |

| 5    | CRT_BLUE         | 6    | KEY        |

| 7    | GND              | 8    | CRTPR#     |

| 9    | DDCSDA           | 10   | GND        |

| 11   | HSYNC            | 12   | CRT_RED#   |

| 13   | VSYNC            | 14   | CRT_GREEN# |

| 15   | DDCSCL           | 16   | CRT_BLUE#  |

## **SDVO-Interface**

X73, 2 x 19 pin Berg Header

| PIN# | SIGNALS TFT PIN# | SIGNA | ALS TFT      |

|------|------------------|-------|--------------|

| 1    | PLTRST#          | 2     | FPPR#        |

| 3    | P12V             | 4     | P12V         |

| 5    | GND              | 6     | GND          |

| 7    | P12V             | 8     | KEY          |

| 9    | VCC              | 10    | VCC          |

| 11   | RXDT             | 12    | SPK          |

| 13   | TXD12            | 14    | N12V         |

| 15   | SDVOCTRL_DATA    | 16    | SDVOCTRL_CLK |

| 17   | SDVOB_INT        | 18    | GND          |

| 19   | SDVOB_INT#       | 20    | GND          |

| 21   | SDVOB_RED        | 22    | GND          |

| 23   | SDVOB_RED#       | 24    | GND          |

| 25   | SDVOB_GREEN      | 26    | GND          |

| 27   | SDVOB_GREEN#     | 28    | GND          |

| 29   | SDVOB_CLKP       | 30    | GND          |

| 31   | SDVOB_CLKN       | 32    | GND          |

| 33   | SDVOB_BLUE       | 34    | GND          |

| 35   | SDVOB_BLUE#      | 36    | GND          |

| 37   | NC               | 38    | NC           |

# PoweredUSB Adapter

X122, 2 x 22 pin Berg Header

| PIN# | SIGNALS | PIN# | SIGNALS |

|------|---------|------|---------|

| 1    | P12V    | 2    | P24V    |

| 3    | P12V    | 4    | P24V    |

| 5    | P12V    | 6    | P24V    |

| 7    | P12V    | 8    | P24V    |

| 9    | P12V    | 10   | P24V    |

| 11   | P12V    | 12   | P24V    |

| 13   | P12V    | 14   | P24V    |

| 15   | P12V    | 16   | P24V    |

| 17   | VCC     | 18   | NC      |

| 19   | VCC     | 20   | KEY     |

| 21   | OVL3    | 22   | NC      |

| 23   | OVL4    | 24   | USBP5   |

| 25   | OVL5    | 26   | USBM5   |

| 27   | VCC     | 28   | GND     |

| 29   | VCC     | 30   | GND     |

| 31   | VCC     | 32   | GND     |

| 33   | USBP4   | 34   | GND     |

| 35   | USBM4   | 36   | GND     |

| 37   | VCC     | 38   | GND     |

| 39   | VCC     | 40   | GND     |

| 41   | USBP3   | 42   | NC      |

| 43   | USBM3   | 44   | NC      |

**USB 3-8** X4, X5, X17, X19, X22 X40, 1 x 6-pin header

| PIN# | SIGNALS USB6 | SIGNALS USB7 | SIGNALS USB8 |

|------|--------------|--------------|--------------|

| 1    | P5V_USB6     | P5V_USB7     | P5V_USB8     |

| 2    | USBM6        | USBM7        | USBM8        |

| 3    | USBP6        | USBP7        | USBP8        |

| 4    | GND          | GND          | GND          |

| 5    | GND          | GND          | GND          |

| 6    | OVL6         | OVL7         | OVL8         |

### **PS/2 MOUSE**

X12, 1 x 4-pin header

| PIN# | SIGNALS PS/2 |

|------|--------------|

| 1    | GND          |

| 2    | MSCKF        |

| 3    | MSDAF        |

| 4    | P5VFKY       |

26

**PCI-ONBOARD**

X6, 80-pin board to board connector

| PIN # SI | GNALS PCI | PIN# | SIGNALS PCI |

|----------|-----------|------|-------------|

| 1        | 12V       | 2    | P12V        |

| 3        | PV3C      | 4    | WOLN        |

| 5        | VCC       | 6    | P5VSB       |

| 7        | PCICLK4   | 8    | PIRQ3N      |

| 9        | PIRQ1N    | 10   | PIRQ2N      |

| 11       | PIRQ0N    | 12   | PCIRNB      |

| 13       | PREQ0N    | 14   | PGNT0N      |

| 15       | GND       | 16   | GND         |

| 17       | AD31      | 18   | AD30        |

| 19       | AD29      | 20   | AD28        |

| 21       | VCC       | 22   | VCC         |

| 23       | GND       | 24   | GND         |

| 25       | AD27      | 26   | AD26        |

| 27       | AD25      | 28   | AD24        |

| 29       | CBE3N     | 30   | AD23        |

| 31       | AD21      | 32   | AD22        |

| 33       | GND       | 34   | GND         |

| 35       | AD19      | 36   | AD20        |

| 37       | AD17      | 38   | AD18        |

| 39       | NC        | 40   | AD16        |

| 41       | FRAMEN    | 42   | GND         |

| 43       | GND       | 44   | CBE2N       |

| 45       | TRDYN     | 46   | IRDYN       |

| 47       | DEVSELN   | 48   | STOPN       |

| 49       | PERRN     | 50   | VCC         |

| 51       | VCC       | 52   | GND         |

| 53       | GND       | 54   | SERRN       |

| 55       | PAR       | 56   | CBE1N       |

| 57       | AD15      | 58   | AD14        |

| 59       | AD13      | 60   | GND         |

| 61       | GND       | 62   | AD12        |

| 63       | AD11      | 64   | AD10        |

| 65       | AD9       | 66   | AD8         |

| 67       | CBE0N     | 68   | AD6         |

| 69       | AD7       | 70   | GND         |

| 71       | RXDTP     | 72   | AD4         |

| 73       | AD5       | 74   | AD2         |

| 75       | AD3       | 76   | AD0         |

| 77       | AD1       | 78   | TXDPCI12    |

| 79       | SPK_PCI   | 80   | VCC         |

## Speaker

X9, 1 x 4-pin dubox header

| PIN# | SIGNALS SP |

|------|------------|

| 1    | SPK        |

| 2    | GND        |

| 3    | RSVB       |

| 4    | VCC        |

## **Power Supply Unit**

X34, 2 x 10-pin header

| PIN# | SIGNALS POW1 | PIN# | SIGNALS POW1 |

|------|--------------|------|--------------|

| 1    | P3V3L        | 2    | PsV3L        |

| 3    | GND          | 4    | VCC          |

| 5    | GND          | 6    | VCC          |

| 7    | GND          | 8    | DCFAILN      |

| 9    | P5USB        | 10   | P12V         |

| 11   | P3V3L        | 12   | N12V         |

| 13   | GND          | 14   | PWRON#       |

| 15   | GND          | 16   | GND          |

| 17   | GND          | 18   | NC           |

| 19   | VCC          | 20   | VCC          |

## X13, 2 x 2 pin header

| PIN# | SIGNALS POWC | PIN# | SIGNALS POWC |

|------|--------------|------|--------------|

| 1    | GND          | 2    | GND          |

| 3    | P12V         | 4    | P12V         |

### Power On

X11, 1 x 4-pin header

| PIN# | SIGNALS PWON |  |

|------|--------------|--|

| 1    | GND          |  |

| 2    | NC           |  |

| 3    | PWRBTN       |  |

| 4    | NC           |  |

|      |              |  |

## **Status Display**

X10, 1 x 4-pin dubox header

| PIN# | SIGNALS LED       |

|------|-------------------|

| 1    | DCF               |

| 2    | NC                |

| 3    | SATA_IDE_BIOS_LED |

| 4    | DCFN              |

## **FAN Connector 1**

X21, 1 x 4-pin header

| PIN# | SIGNALS FAN1 |

|------|--------------|

| 1    | GND          |

| 2    | P12V         |

| 3    | FAN_RPM1     |

| 4    | FAN_PWM1     |

### **FAN Connector 2**

X14, 1 x 4-pin header

| PIN# | SIGNALS FAN2 |  |  |

|------|--------------|--|--|

| 1    | GND          |  |  |

| 2    | P12V         |  |  |

| 3    | FAN_RPM2     |  |  |

| 4    | FAN_PWM2     |  |  |

**POS Board**

X3, 2 x 50-pin header

| PIN#   | SIGNALS          | PIN#     | SIGNALS      |

|--------|------------------|----------|--------------|

| 1      | P3V3C            | 2        | P3V3C        |

| 3      | P3V3C            | 4        | WOL#         |

| 5<br>7 | P3V3C            | 6        | P3V3C        |

| 7      | PLOCK#           | 8        | PIRQ3#       |

| 9      | PIRQ1#           | 10       | PIRQ2#       |

| 11     | PIRQ0#           | 12       | PCIRNC       |

| 13     | PREQ3#           | 14       | PGNT0#       |

| 15     | GND              | 16       | GND          |

| 17     | AD31             | 18       | AD30         |

| 19     | AD29             | 20       | AD28         |

| 21     | VCC              | 22       | VCC          |

| 23     | GND              | 24       | GND          |

| 25     | AD27             | 26       | AD26         |

| 27     | AD25             | 28       | AD24         |

| 29     | CBE3N#           | 30       | AD23         |

| 31     | AD21             | 32       | AD23<br>AD22 |

| 33     | GND              | 34       | GND          |

| 35     | AD19             | 36       | AD20         |

| 37     | AD19<br>AD17     | 38       | AD18         |

| 39     | SERIRQ           | 40       | AD16         |

| 41     | FRAME#           | 42       | GND          |

| 43     | GND              | 44       | CBE2#        |

| 45     | TRDY#            | 44<br>46 | IRDY#        |

| 45     |                  | 48       | STOP#        |

|        | DEVSEL#<br>PERR# |          |              |

| 49     |                  | 50<br>53 | VCC          |

| 51     | VCC              | 52<br>54 | GND          |

| 53     | GND              | 54       | SERR#        |

| 55     | PAR              | 56       | CBE1#        |

| 57     | AD15             | 58       | AD14         |

| 59     | AD13             | 60       | GND          |

| 61     | GND              | 62       | AD12         |

| 63     | AD11             | 64       | AD10         |

| 65     | AD9              | 66       | AD8          |

| 67     | CBE0#            | 68       | AD6          |

| 69     | AD7              | 70       | GND          |

| 71     |                  | 72       | AD4          |

| 73     | AD5              | 74       | AD2          |

| 75     | AD3              | 76       | AD0          |

| 77     | AD1              | 78       |              |

| 79     | VCC              | 80       | VCC          |

| 81     | GND              | 82       |              |

| 83     | PCICLK1          | 84       | PGNT2#       |

| 85     | PCICLK2          | 86       | PGNT3#       |

| 87     | PCICLK3          | 88       |              |

| 89     | PREQ1#           | 90       | P5VSB        |

| 91     | PREQ2#           | 92       | P5VSB        |

| 93     | N12V             | 94       |              |

| 95     | P12V             | 96       | P12V         |

| 97     | P12V             | 98       | P12V         |

| 99     | TXD5             | 100      | RXD5         |

# **BIOS Setup**

The Celeron M / Pentium M main board comes with a Phoenix BIOS chip that contains the ROM Setup information of your system. This chip serves as an interface between the processor and the rest of the main board's components. This section explains the information contained in the Setup program and tells you how to modify the settings according to your system configuration.

Even if you are not prompted to use the Setup program, you might want to change the configuration of your system in the future. For example, you may want to enable the Security Password Feature or make changes to the power management settings. It will then be necessary to reconfigure your system using the BIOS Setup program so that the system can recognize these changes and record them in the CMOS RAM or the FLASH ROM. All setup data is stored in a non volatile memory (CMOS RAM). If you remove the CMOS battery, all parameters will be lost.

#### Standard BIOS Version

The BIOS ROM of the system holds the Setup utility. When you turn on the system, it will provide you with the opportunity to run this program. This appears during the Power-On Self Test (POST). Press <F2> to call the Setup utility. If you are a little bit late pressing the mentioned key, POST will continue with its test routines, thus preventing you from calling Setup. If you still need to call Setup, reset the system by pressing <Ctrl> + <Alt> + <Delete>. You can also restart by turning the system off and then on again. But do so only if the first method fails.

The Setup program has been designed to make it as easy as possible. It is a menu-driven program, which means you can scroll through the various sub-menus and make your selections among the predetermined choices.

When you invoke Setup, the main program screen will appear. On the following pages you will read more information about the Setup entries.

Because the BIOS software is constantly being updated, the following BIOS screens and descriptions are for reference purposes only and may not reflect your BIOS screens exactly.

#### **BIOS Menu Bar**

The top of the screen has a menu bar with the following sections:

INFO Use this menu for information only

MAIN Use this menu to make changes to the basic system configuration.

ADVANCED Use this menu to enable and make changes to the advanced features.

SECURITY Use this menu to enable a supervisor password.

POWER Use this menu to configure and enable Power Management features.

BOOT Use this menu to configure the default system device used to locate and

load the Operating System.

EXIT Use this menu to exit the current menu or specify how to exit the Setup

program.

To access the menu bar items, press the right or left arrow key on the keyboard until the desired item is highlighted.

## **Legend Bar**

At the bottom of the Setup screen you will notice a legend bar. The keys in the legend bar allow you to navigate through the various setup menus. The following table lists the keys found in the legend bar with their corresponding alternates and functions.

| Navigation Key(s)                             | Description of Functions                                           |

|-----------------------------------------------|--------------------------------------------------------------------|

| <f1></f1>                                     | Displays the General Help screen from anywhere in the BIOS Setup.  |

| <esc></esc>                                   | Jumps to the Exit menu or returns to the main menu from a submenu. |

| $\leftarrow$ or $\rightarrow$ (keypad arrows) | Select the menu item to the left or right.                         |

| ↑ or ↓ (keypad arrows)                        | Moves the highlight up or down between fields.                     |

| - (minus key)                                 | Scrolls backward through the values for the highlighted field.     |

| + (plus key) or spacebar                      | Scrolls forward through the values for the highlighted field.      |

| <enter></enter>                               | Brings up a selection menu for the highlighted field.              |

| <home> or <pgup></pgup></home>                | Moves the cursor to the first field.                               |

| <end> or <pgdn></pgdn></end>                  | Moves the cursor to the last field.                                |

| <f9></f9>                                     | Loads the default configuration into Setup.                        |

| <f10></f10>                                   | Saves changes and exits Setup.                                     |

#### **General Help**

In addition to the Item Specific Help window, the BIOS setup program also provides a General Help screen. This screen can be called from any menu by simply pressing <F1> or the <Alt> + <H> combination. The General Help screen lists the legend keys with their corresponding alternates and functions.

#### Scroll Bar

When a scroll bar appears to the right of a help window, it indicates that there is more information to be displayed that will not fit in the window. Use <PgUp> and <PgDn> or the up and down keys to scroll through the entire help document.

Press <Home> to display the first page, press <End> to go to the last page. To exit the help window, press <Enter> or <Esc>.

#### Sub-Menu

Note that a right pointer symbol appears to the left of certain fields. This pointer indicates that a submenu can be launched from this field. A sub-menu contains additional options for a field parameter. To call a sub-menu, simply move the highlight to the field and press <Enter>. The sub-menu then will appear immediately. Use the legend keys to enter values and move from field to field within a submenu just as you would do within a menu. Use the <Esc> key to return to the main menu.

Take some time to familiarize yourself with each of the legend keys and their corresponding functions. Practice navigating through the various menus and sub-menus. If you accidentally make unwanted changes to any of the fields, use the set default hot key <F9>. While moving around through the Setup program, note that explanations appear in the Item Specific Help window located to the right side of each menu. This window displays the help text for the currently highlighted field.

## Info screen

When the Setup program is accessed, the following screen appears:

| Product name:<br>Bios version: | F2-CPU Basic<br>xx/yy mm/dd/yyyy |

|--------------------------------|----------------------------------|

| Ethernet MAC-Address:          | 00-03-56-xx-yy-zz                |

| System:                        |                                  |

| Main board:                    |                                  |

| Power Supply:                  |                                  |

This screen is for information only. There is nothing that could be changed within Setup. All information are intended to facilitate the support of your system.

#### Product name:

This text is fixed for your Celeron M / Pentium M main board with standard BIOS. This board is also called "F2-CPU-Standard".

#### **Bios version:**

The Bios version is displayed in the release format xx/yy, followed by date of release in international format.

## **Ethernet MAC-Address:**

The Ethernet MAC-Address of the Onboard LAN Controller is displayed at this line.

## System, Main board, Power Supply:

The default placeholders may be replaced by specific data from factory, describing configuration, serial number etc. for each device.

## Main Menu

|      | System Time:<br>System Date:                                                      | [08:14:46]<br>[07/14/2004]              |

|------|-----------------------------------------------------------------------------------|-----------------------------------------|

| AAAA | IDE Channel 0 Master IDE Channel 0 Slave IDE Secondary/Master IDE Secondary/Slave | [None]<br>[None]<br>[41174MB]<br>[None] |

|      | Extended Memory:                                                                  | 374 MB                                  |

## System Time [XX: XX: XX]

Sets your system to the time that you specify (usually the current time). The format is hour, minute, second. Valid values for hour, minute, and second are: Hour: (00 to 23), Minute: (00 to 59), Second: (00 to 59). Use the <Tab> or <Shift> + <Tab> keys to move between the hour, minute, and second fields.

#### System Date [XX/XX/XXXX]

Sets your system to the date that you specify (usually the current date). The format is month, day, year. Valid values for month, day, and year are: Month: (1 to 12), Day (1 to 31), Year: (up to 2079).

Use the <Tab> or <Shift> + <Tab> keys to move between the month, day, and year fields.

## **Primary & Secondary Master/Slave**

The first 2 lines are info lines about the attached S-ATA hard disks, while the next two are using for the older P\_ATA disks.

**Note**: Before attempting to configure a hard disk drive, make sure you have the configuration information supplied by the manufacturer of the drive. Incorrect settings my cause your system not to recognize the installed hard disk. To allow the BIOS to detect the drive type automatically, select [Auto].

| Туре:                                                                                                               | [Auto]                                                             |

|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| LBA Format<br>Total Sectors<br>Maximum Capacity                                                                     | 80418240<br>41174MB                                                |

| Multi-Sector Transfers:<br>LBA Mode Control:<br>32 Bit I/O:<br>Transfer Mode:<br>Ultra DMA Mode<br>SMART Monitoring | [16 Sectors] [Enabled] [Disabled] [Fast PIO 4] [Mode 5] [Disabled] |

## Type [Auto]

Select [Auto] to automatically detect an IDE hard disk drive. If automatic detection is successful, the correct values will be filled in for the remaining fields on this sub-menu. If automatic detection fails, your hard disk drive may be too old or too new. You can try updating your BIOS or enter the IDE hard disk drive parameters manually.

After the IDE hard disk drive information has been entered into BIOS, new IDE hard disk drives must be partitioned (e.g. with FDISK) and then formatted before data can be read from and written to. Primary IDE hard disk drives must have its partition set to active (also possible with FDISK).

Other options for the Type field are: [None] to disable IDE devices.

**IMPORTANT**: If your hard disk was already formatted on an older previous system, incorrect parameters may be detected. You will need to enter the correct parameters manually or use low-level format if you do not need the data stored on the hard disk. If the parameters listed differ from those used when the disk was formatted, the disk will not be readable. If the auto detected parameters do not match those that should be used for your disk you should enter the correct ones manually by setting [User].

## [User]

Manually enter the number of cylinders, heads and sectors per track for your drive. Refer to your drive documentation or to the label on the drive. If no drive is installed or if you are removing a drive and not replacing it, select [None].

## **Cylinders**

This field configures the number of cylinders. Refer to your drive documentation to determine the correct value to enter into this field.

To make changes to this field, the Type field must be set to [User].

#### Heads

This field configures the number of read/write heads. Refer to your drive documentation to determine the correct value to enter into this field.

To make changes to this field, the Type field must be set to [User].

#### Sector

This field configures the number of sectors per track. Refer to your drive documentation to determine the correct value to enter into this field.

To make changes to this field, the Type field must be set to [User].

### **Maximum Capacity**

This field shows the drive's maximum capacity calculated automatically by the BIOS from the drive information you entered.

#### **Multi-Sector Transfers [Maximum]**

This option automatically sets the number of sectors per block to the highest number supported by the drive. This field can also be configured manually. Note that when this field is configured automatically, the value set may not always be the fastest value for the drive. Refer to the documentation that came with your hard drive to determine the optimal value and set it manually.

To make changes to this field, the Type field must be set to [User]. Configuration options: [Disabled] [2 Sectors] [4 Sectors] [8 Sectors] [16 Sectors].

## LBA Mode Control [Enabled]

Select the hard disk drive type in this field. When Logical Block Addressing is enabled, 28-bit addressing of the hard drive is used without regard to cylinders, heads, or sectors. Note that Logical Block Access may decrease the access

speed of the hard disk. However, LBA Mode is necessary for drives with more than 504MB of storage capacity. Configuration options: [Enabled] [Disabled].

32 Bit I/O [Disabled]

This field setting enables or disables the 32 Bit IDE data transfers. Configuration options: [Disabled] [Enabled].

## **Transfer Mode**

This option lets you set a PIO (Programmed Input/Output) mode for the IDE device. Modes 0 trough 4 provide successively increased performance. Configuration options: [Standard] [Fast PIO 1] [Fast PIO 2] [Fast PIO 3] [Fast PIO 4] [FPIO 3 / DMA 1] [FPIO 4 / DMA 2].

Other options for Type are:

[CD-ROM] for IDE CD-ROM drives

After using the legend keys to make your selections in this sub-menu, press the <Esc> key to exit back to the Main menu. When the Main menu appears, you will notice that the drive size is indicated in the field for the hard disk drive that you just configured.

## **SMART Monitoring**

This field informs about the enabling of the S.M.A.R.T. (Self-Monitoring, Analysis and Reporting Technology) system which utilizes internal hard disk drive monitoring technology. This field is read only.

## **Extended Memory: XXX MB**

This field displays the amount of extended memory detected by the system during bootup. You do not need to make changes to this field. This is a display only field.

#### **Advanced Menu**

Reset Configuration Data: [No]

Speaker Volume [High]

Large Disk Access Mode: [DOS]

Legacy USB Support: [Enabled]

Internal LAN Controller: [Enabled]

Onboard LAN Boot Prom: [Disabled]

QuickBoot Mode [Disabled]

Fan Control: [Max Cooling]

- Chipset Configuration

- > I/O Device Configuration

- DMI Event Logging

## **Reset Configuration Data [No]**

[Yes] erases all configuration data in a section of memory for ESCD (Extended System Configuration Data) which stores the configuration settings for non-PnP Plug-in devices. Configuration options: [No] [Yes]

If you are facing problems after adding or removing any hardware components to the system it might be wise to select the [Yes] option once. This allows the BIOS to reconfigure available hardware resources.

## **Speaker Volume [High]**

This field is for the volume control of the installed speaker. Configuration options [High] [Middle] [Low].

#### Large Disk Access Mode [DOS]

For UNIX, Novell Netware, or other operating systems you have to select [Other]. For DOS or Windows use the value of default [DOS]. Configuration options: [DOS] [Other].

#### Legacy USB Support [Disabled]

This motherboard supports Universal Serial Bus (USB) devices. The default of [Disabled] the USB controller is disabled no matter whether you are using a USB device or not. The enabling of the controller will run with the help of a USB compliant operating system like Windows XP or else. If the point stands on [Enabled] the legacy USB support from the BIOS is started. Now it is possible to use a USB keyboard to start this setup or with the standard DOS environment. If you like to use a USB-Floppy disk or a USB CD-ROM device for booting, you have to enable this setup point and after detecting of this USB device from the BIOS, you have to switch the boot order to the appropriate device. Configuration Options: [Disabled] [Enabled]

Note: Selecting Legacy USB Support [Disabled] has impact on "Boot Order" in "BOOT" Menu, resetting this field do its default value and locking it. See "Boot Order" description.

#### **Internal LAN Controller [Enabled]**

This point switches physical on or off the Onboard LAN Controller. Configuration Options: [Disabled] [Enabled]

## **Onboard LAN Boot Prom [Disabled]**

This point switches on or off the PXE PROM from the onboard LAN Controller. Configuration Options: [Disabled] [Enabled]

### QuickBoot Mode [Disabled]

Allows the system to skip certain tests while booting. This will decrease the time needed to boot the system. Configuration options: [Enabled] [Disabled]

## Fan Control [Max Cooling]

This setup mode will control the rotating of the PWM-Fans due to actual CPU-Temperature if setting to Automatic. With Max Cooling is the speed of the fans always high. Configuration Options: [MAX Cooling] [Automatic]

## **Chipset Configuration**

| SMART Device Monitoring: | [Disabled] |  |

|--------------------------|------------|--|

| Boot-Video Device:       | [Onboard]  |  |

| USB 2.0 Support          | [Enabled]  |  |

## **SMART Device Monitoring [Disabled]**

This field controls the enabling of the S.M.A.R.T. (Self-Monitoring, Analysis and Reporting Technology) system which utilizes internal hard disk drive monitoring technology. Configuration options: [Disabled] [Enabled].

### **Boot-Video device [Onboard]**

The main board has an Onboard graphic adapter. If your computer has additionally installed a PCI VGA card additionally installed, this field allows you to select which of the cards will act as your primary display card. The default, [Onboard], allows your PCI card to take precedents only when no onboard bridge is detected. [PCI-Slot] uses the PCI VGA adapter card as primary card. Configuration options: [Onboard] [PCI-Slot].

#### **USB 2.0 Support [Enabled]**

Using USB devices complying 2.0 standard, let this field be Enabled. Due to lack of appropriate drivers you may switchback to Disabled. Configuration options: [Disabled] [Enabled].

## I/O Device Configuration

Serial port A: [Enabled]

Base I/O address: [3F8]

Interrupt: [IRQ 4]

Serial port B: [Enabled]

Base I/O address: [2F8]

Interrupt: [IRQ 3]

Touch Screen Routing: [TFT Touch to COM2]

## Serial port A [Enabled], Serial port B [Enabled]

These fields don't configure the Serial ports directly. Both ports are always enable.

#### Base I/O address

This field sets the address for the onboard serial connectors. Configuration options: [3F8] [3E8] [2F8] [2E8].

## Interrupt

Combine the Base I/O address with an interrupt. Configuration options: [IRQ 4] [IRQ 3]

#### **Touch Screen Routing [TFT Touch to COM2]**

Using a Touch Screen you may select routing it to a serial interface using hardware lines instead of COM1 or COM2.

Configuration Options: [No Routing] [TFT Touch to COM1] [TFT Touch to COM2] [TFT Touch to COM5] [PCI Touch to COM1] [PCI Touch to COM2] [TFT&PCI Touch to COM (1&2)]

## **DMI Event Logging**

Event log capacity Space available

Event log validity Valid

View DMI event log [Enter]

Clear all DMI event logs [No]

Event Logging [Enabled]

Mark DMI events as read [Enter]

Desktop Management Interface (DMI) is a method of managing computers in an enterprise. Using DMI, a system administrator can obtain the types, capabilities, operational status, installation date and other information about the system components. An event log is a fixed-length area within a non-volatile storage element.

## View DMI event log [Enter]

This setup point is useful to display the recorded DMI events like a defect floppy disk controller or anything else. If there is an error stored, the BIOS will display a message every time the system is starting up.

## Clear all DMI event logs [No]

With this point it is possible to clear all the recorded DMI events manually.

## **Event logging [Enabled]**

If you do not use the DMI event logging, it is possible to shut off the recording mechanism of errors.

## Mark DMI events as read [Enter]

If you dislike the BIOS message at system starting up but you like to have the errors recorded, mark all DMI events as read. With the next start up of the system, the BIOS would not display a message.

## **Security Menu**

| Supervisor Password Is: | Clear   |

|-------------------------|---------|

| Set Supervisor Password | [Enter] |

#### **Set Supervisor Password**

This field allows you to set the password. Highlight the field and press <Enter>.

Type a password and press <Enter>, you can type up to eight alphanumeric characters. Symbols and other characters are ignored. To confirm the password, type the password again and press <Enter>. The password is now set to [Enabled]. This password allows full access to the BIOS Setup menu.

To clear the password, highlight this field and press <Enter>. The same dialog box as above will appear. Press <Enter> and the password will be set to

[Disabled].

## **Power Menu**

The Power menu allows you to reduce power consumption. This feature turns off the video display and shuts down the hard disk after a period of inactivity.

|   | After Power Failure:                                 | [Stay Off]                             |

|---|------------------------------------------------------|----------------------------------------|

|   | Wake On LAN:<br>Wake On Modem Ring:<br>Wake On Time: | [Disabled]<br>[Disabled]<br>[Disabled] |